ub8优游国标

ub8优游国标时间: 2023-12-17 16:54:08 | 作者: 黑色网格防静电胶带

第 2 部分研究你的元件选择怎么样影响低泄漏电路的性能,并讨论噪声如何渗透到低泄漏设计中。

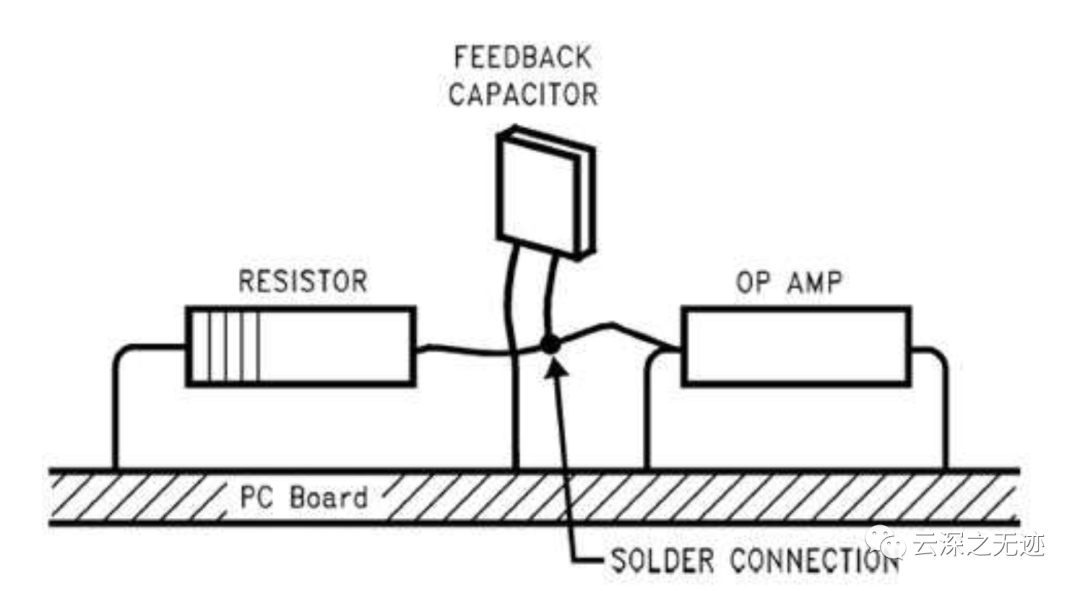

经典的低电流技术是“空中”布线技术,其中关键路径或电路节点中的组件引线在电路板上方焊接在一起。这些元件引线和走线不与电路板接触,因此有效消除了PC板的影响。Teflon 支座端子可用于支撑大型组件或人口密集的节点。组件下方的区域应该是坚固的、的防护平面。

该技术提供了最低的泄漏、最低的杂散电容和最佳的整体低电流性能,但需要手工组装,并且在大规模生产或有限的空间区域中不容易实现。整个电路不必放置在电路板上方,只需放置关键节点即可。在上面的图 1 中,电路的反相节点(包括输入信号、反馈电阻电容器)都直接焊接到运放反相端子的弯曲腿上。 使用双通道的第二个通道 这里有一个小技巧:如果你正在设计使用非反相配置的电路,请使用双通道的第二个(“B”)通道作为主放大器。

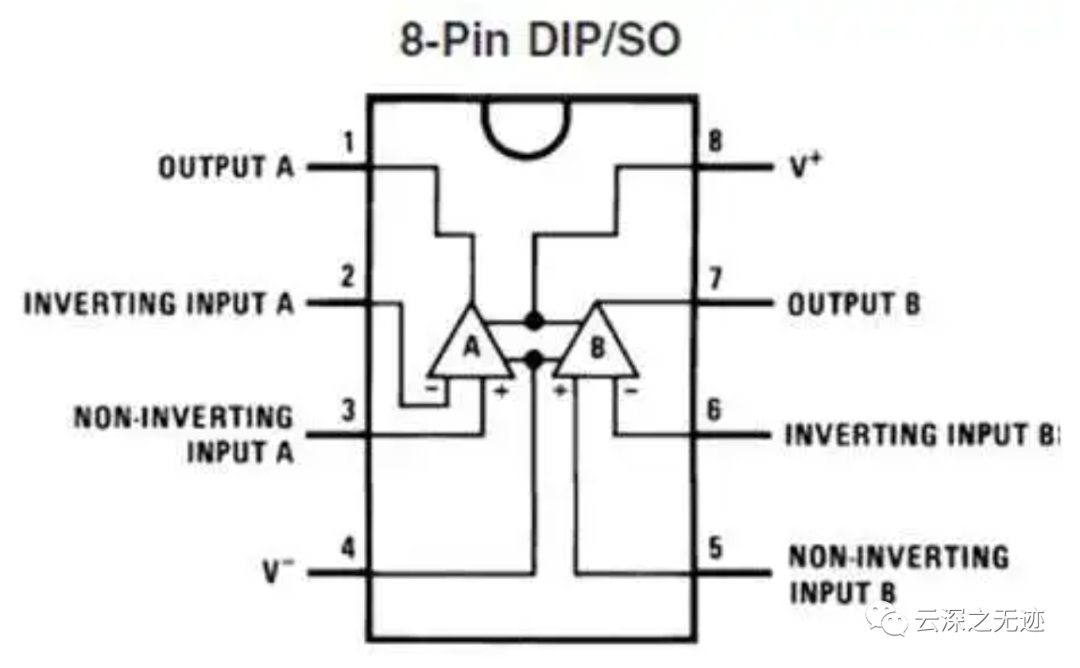

在标准双引脚排列中,“B”同相输入距离负电源引脚较远,并且也受到反相引脚向北“保护”,并且输入位于封装的一角,以便于安装与源的连接。在 V- 和“B”非反相引脚之间还有更多的空间来运行保护走线。“A”通道放大器可用作保护驱动器。 单引脚排列遇到与“A”通道相同的问题,其中非反相输入靠近电源。除了微小的单选项之外,如果单版本和双版本都采用相同的 8 引脚封装,则使用双版本可能更有利。 小包装可能不太好…

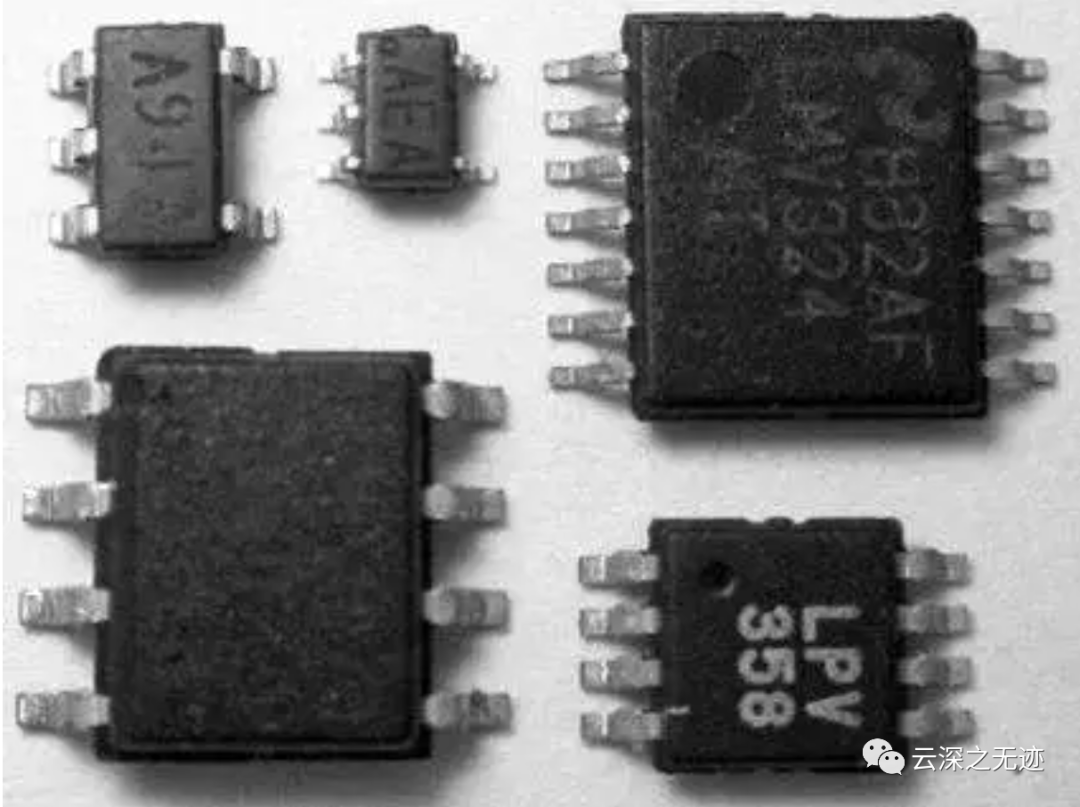

图 3:小型封装比较(顶行)SOT-23、SC-70、TSSOP-14,(底行)SOIC-8 和 MSOP-8 引线间距较窄的封装往往具有较高的泄漏。这主要是因为引线间距很小并且更靠近电源线和其他引脚。电路板每平方的电阻率保持不变,但将焊盘移得更近会缩短距离,以此来降低电阻率。 此外,更紧密的螺距会更快地积聚污垢,并且在这些紧密的螺距下更难以正确清洁。如果空间不是很宝贵的线 更好的少数情况之一。旧的DIP封装仍然是这方面最好的封装。出于同样的原因,SOT-23 单路优于 SC-70 单路。 设计和布局建议以下是自己的设计时需要牢记的一些一般性建议。 保护走线应围绕所有输入级。内层和底层也保护PC板。输出不需要保护,因为它是低阻抗的,但它应该与输入级屏蔽。

保护间距和输入电容之间需要权衡。保护线和输入走线之间的间隙越大,输入电容就越小。 最大限度地减少输入表面积,以减少杂散电容和电离冲击的影响。由于在皮安信号电平下,IR 压降并不是一个大问题,而且速度通常较低,因此请使用尽可能窄的走线宽度以减少杂散。使用最小尺寸的 SMT 焊盘来最大化焊盘之间的空间。 固定所有松散的电线。灵敏的高阻抗电路能“看到”导线的移动 (ΔC)。在防护区域内,跳线或互连线应(无绝缘层,最好是镀锡实心铜)。

去除阻焊层的印刷电路板区域应封闭在密封防护罩或防护罩内,以防止潮湿和灰尘。 仅根据需要在导体周围使用尽可能多的聚四氟乙烯或其他在允许电压下不导电的材料。守卫其余区域。请注意高压所需的间距。 注意板上的塑料和胶带的使用。使用防静电导电胶带。 陶瓷电容器是压电电容器,机械振动和噪音会在电容器上产生电荷。在输入、集成、反馈或偏置网络中使用陶瓷电容时要小心。 整个外壳应环境密封,当湿度有几率会成为问题时,应使用干燥剂包。作为定期校准或现场服务的一部分,用户或计量实验室应易于更换这些包。

最大限度地减少电路板的弯曲和应力。使用多个板安装点或支架,并且不仅通过板支持外部用户控件和连接器。 正如文章开头提到的,与“传统”电路相比,设计成功的亚皮安级电路需要不同的设计实践。通过遵循上述简单的建议,就能取得很高的首次成功率。 设计挑战作者的任务是提高 LMP7721 低输入偏置电流 CMOS运算放大器评估板的性能。该电路板需要展示器件的近飞安输入电流性能,同时仍使用标准低成本 FR4 电路板和传统的表面贴装组件。该板还必须支持多种电路配置。

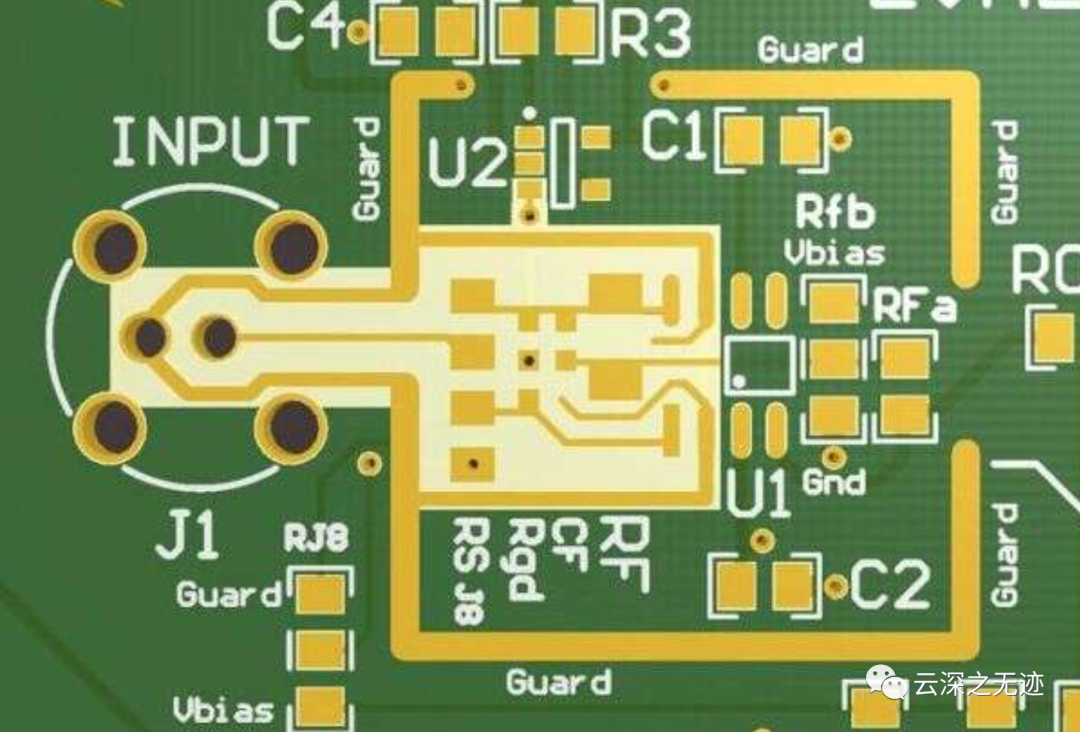

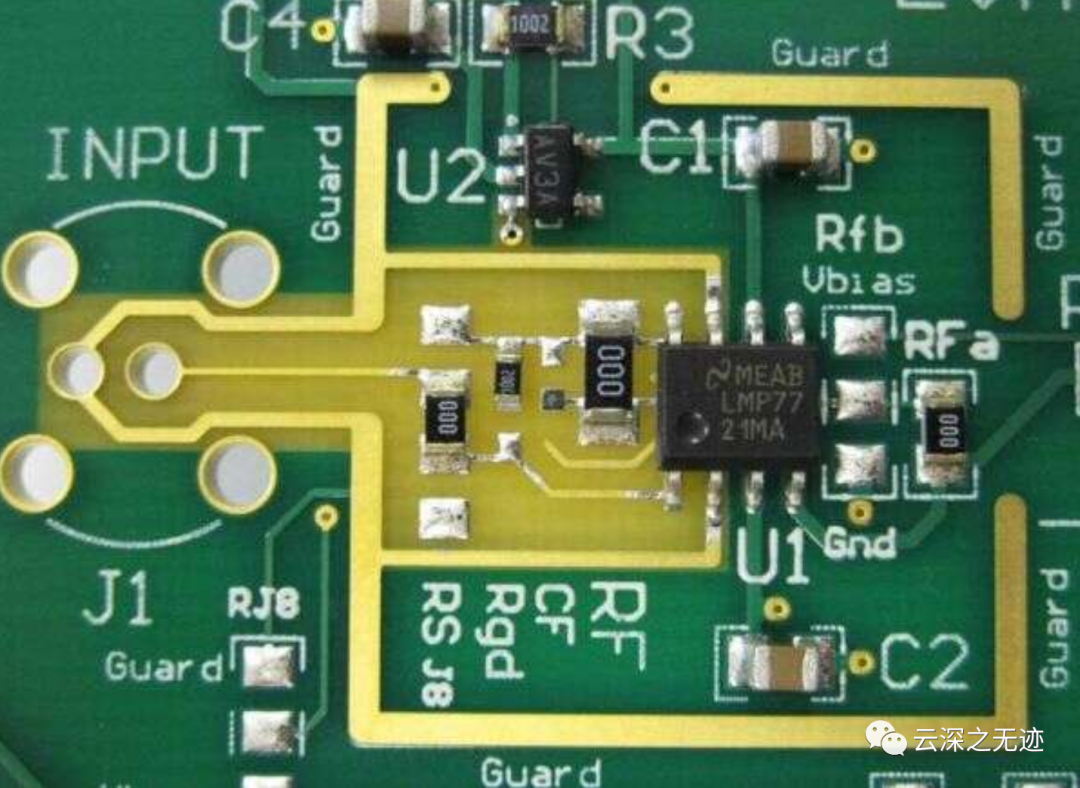

图 4:LMP7721 评估板 第一步是最小化输入表面积。这减少了杂散输入电容,使输入更容易保护,最大限度地减少静电耦合和电离冲击的影响。

在输入电路周围添加了广泛的缓冲保护系统。在周边添加了宽迹线,以允许在整个电路周围安装可选的金属屏蔽。 输入走线和所有敏感反馈组件均位于较小防护箱的周边内。较大的外部裸铜方盒用于焊接在金属防护罩上,以覆盖整个输入电路。 LMP7721 具有独特的引脚排列,通过保护引脚(引脚 2 和 7)将输入引脚(引脚 1 和 8)与电源和输出引脚分开。这些引脚连接到防护装置,以提供一直到引线框架级别的防护。 该区域的阻焊层也被去除,以减少电荷积累。

为了最大限度地减少输入电容并减少输入的物理表面积,输入走线非常薄,并且电阻焊盘具有跳线的双重作用。 该布局旨在通过更改一些电阻器和跳线电阻器来适应反相、非反相和缓冲器配置(照片中显示了“缓冲器”配置)。 通常,每个电阻器,甚至是未使用的电阻器选项,都会有自己的焊盘。这将使几个未连接的焊盘“浮动”而未使用。 相反,焊盘的布局使得将电阻器放置在适当的位置就可以完成电路并选择配置。 其结果是一个非常紧密、紧凑的布局,并且暴露的输入导体最少。

当然,专用电路会更小、更紧凑。 正确清洁电路板正确清洁电路板对于提供预期的亚皮安性能至关重要。 与传统方法相比,正确清洁电路板和组件需要一些额外的步骤。剩余的助焊剂残留物、水分和清洁残留物会严重降低低电流性能。 不建议在最终清洁中使用“免洗”喷雾助焊剂。水溶性助焊剂仍然会留下一层薄膜。 对受保护区域内的组件进行任何返工后,应重新清洁电路板。 应使用异丙醇或甲醇清洗电路板,确保清除电路板上所有残留的水分。应擦洗元件引线之间的区域,并彻底冲洗表面安装器件下方的区域。

在上图中,使用酸刷擦洗电路板,该酸刷已将长刷毛切成短长度以增加刷毛硬度。这是为了更好地擦洗设备引脚之间。 “标准”清洁后,建议的扩展清洁程序为: 除去所有水分——否则它会与酒精发生反应并留下白色粉末状沉积物。 用酒精(80% 或更高)淹没板。

用硬刷擦洗器件引线、连接器之间以及周围的组件。 再次用酒精冲洗以清除碎片并用压缩空气吹掉多余的碎片。还可在 SMT 设备下进行冲洗和吹气。不要忘记板的底部! 快速擦干,然后用干净的毛巾擦干。 烘烤板以除去剩余的水分。 清洁后,只能拿住板子的边缘,不要触摸防护区域内的任何东西。

避免在板上呼吸,因为呼吸中的盐水会严重降低性能。如果保护区内的部件发生任何变化,应重复清洁程序。 电路板应存放在密封的容器或袋子中,最好带有干燥剂包。 验证电路板的性能组装和清洁电路板后,必须测量电路板的性能。设计了一个简单的测试来检查性能。 对于反相放大器或跨阻放大器,只需断开电源并观察基线“零”电平即可测量泄漏。任何高于理论基线水平的水平很可能是由于泄漏造成的。然而,由于这些电路包含大电阻,因此由于噪声,解析毫微微安可能会很困难。

因此,选择非反相缓冲器配置来测试电路板性能。 为了测试同相输入,使用了开路“浮动”测试。漏电流在输入电容上积分。根据所得的漂移率和已知的输入电容值,可以计算出漏电流。 同相输入“浮动”测试相当简单。输入暂时用电线接地,然后通过快速从输入上拔掉接地线来打开。

然后允许输入“浮动”未连接,同时定期测量输出电压以计算电流。 测试所需的设备相当简单,只需要一个数字万用表和一个秒表或类似的间隔记录装置。如果有数字示波器,也可用于此功能。 设置该设置被封装在一个钢制咖啡罐中,并用金属盖或铝箔(不是塑料盖)覆盖。

图 8:咖啡罐内的测试电路。(能够正常的看到测试线连接到输入端) 一根长而薄的接地非绝缘总线穿过顶部的一个小孔,插入输入端。该电线 左侧所示。电线末端已弯曲成狭窄的“V”形,并摩擦配合到输入垫中,因此能快速轻松地拉出。 要开始测试,请将电线从外壳中完全拉出以打开输入并开始测试。以 10 秒的间隔记录输出电压,持续 500 秒。

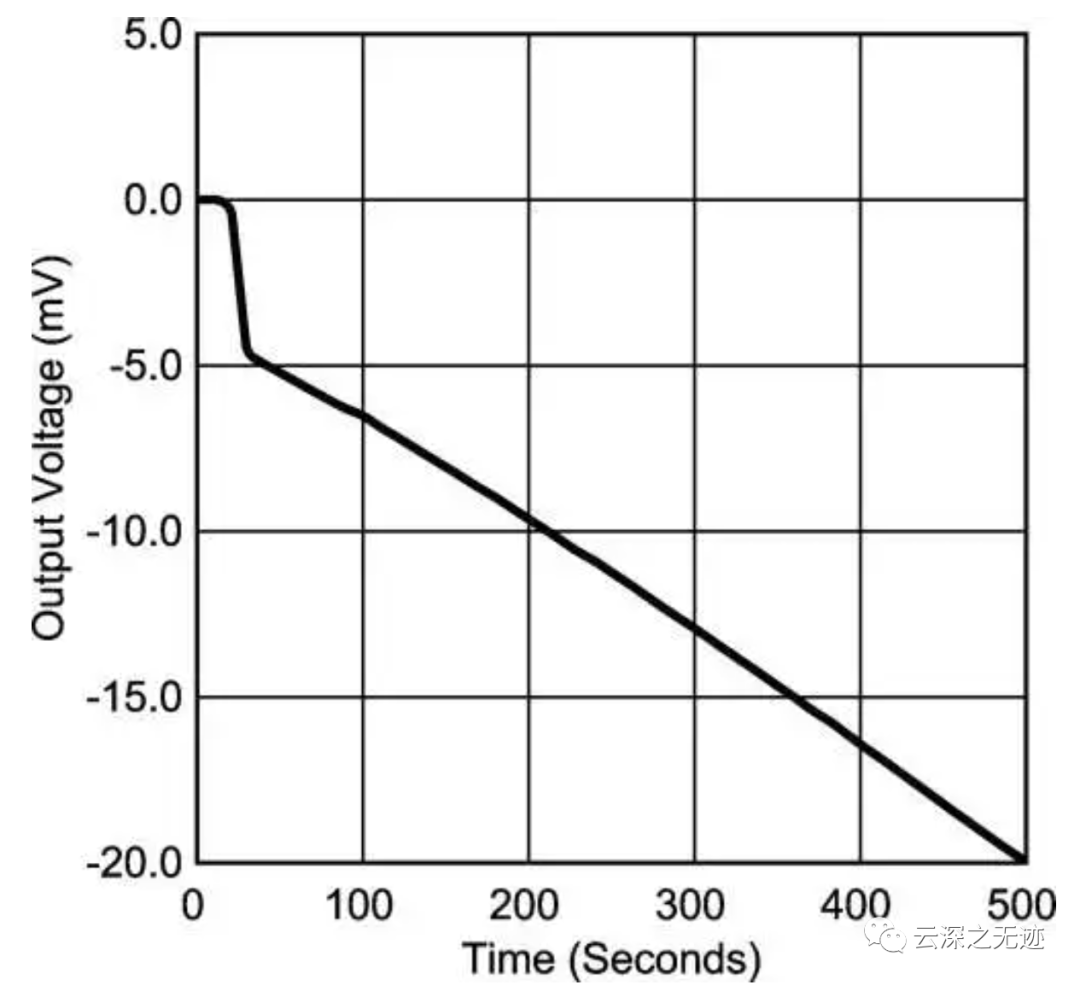

图 9 显示了结果。在前两次采样后(20 秒),将电线拉出。可见的是拉出电线后输出的初始跳跃(由于机械干扰)。大约 40 秒后,输出稳定到每秒小于 1mV 的恒定漂移率。 使用已知的输入电容(该板之前测量的电容约为 12pF)以及测得的电压和时间变化,能够正常的使用以下简单公式对输出电压随时间的变化进行积分,从而计算出输入漏电流: i = (Δv / Δt) * C 看图9,我们大家可以粗略计算出平均输入电流。输出从 200 秒时的 -10mV 变为 500 秒时的 -20mV。ΔV为-10mV,ΔT为300秒。将这些值代入公式即可得出约飞安级的泄漏。 (-10mV / 300秒) * 12.2pF = -1.2fA 这对于 FR4 板来说是非常好的性能! 测量输入电容输入电容受多种因素影响。最突出的是放大器的输入电容和走线电容。 大多数运算放大器的输入电容范围为 2pF 至 15pF,“低噪声”CMOS 器件的输入电容高达 40pF。插座、PCB走线、保护元件、反馈元件、连接器和电缆可以显着增加该值。

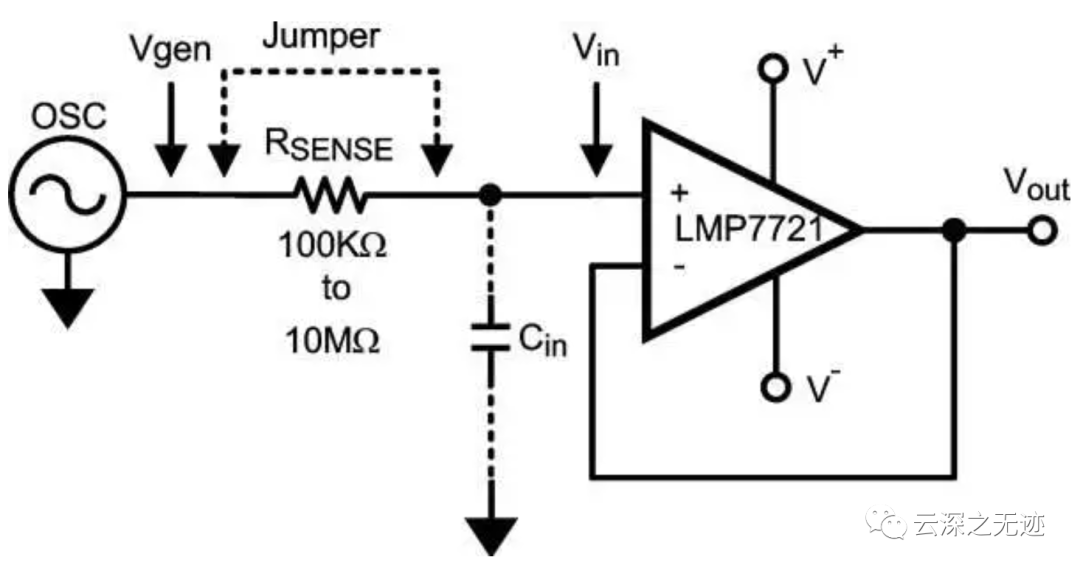

实际的总电容值将取决于您的个人电路和布局。 了解电路的输入电容对于电路设计和电流测量都至关重要。测量电容的方法有多种,例如使用电容计,但这种方法存在问题。 大多数电容表都基于“电桥”或交流源测量配置,并且不能将其端子之一接地。一些手持式数字万用表具有电容功能,您可通过手持设备的“浮动”特性,但这些仪表通常在皮法范围内不准确,和/或在“浮动”时容易受到噪声拾取或邻近效应的影响。 一种简单的技术涉及使用与输入串联的大串联电阻(100K 至>

10M)和正弦波信号发生器(10Hz 至 ~100KHz)。

图 10:输入电容测试电路 RC 极由大串联测试电阻 (Rsense) 和输入电容 (Cin) 创建。

为了找到这个极点,交流信号通过串联电阻馈送,同时扫描发生器频率,直到监控的输出幅度下降到参考频率幅度的 70.7% (-3dB)。通过了解极点频率和电阻值,就可以计算出输入电容。 为了执行测试,在检测电阻器上放置一个临时跳线以将其短路。将示波器或交流电压表连接到放大器输出 (Vout),然后将发生器设置为低参考频率;例如 10Hz,并将幅度设置为一些方便的值,例如 100mV (Vgen)。 移除测试电阻器上的跳线,扫描发电机频率,直到输出电压降至初始 Vin (70.7mV) 的 70.7%,并记录发电机频率。 现在频率和电阻已知,因此现在能够准确的通过 RC 公式计算电容: Cin = 1 / (6.28 * R * F) 例如,使用 10Mohm 串联电阻,我们得知 100mV 输出在 1.305kHz 时降至 70.7mV。所以: Cin = 1 / (6.28 * 10M * 1305) 辛=12.2pF 此测量有几点需要注意。

第一个是检测电阻器两端的杂散电容,对于 1/4 瓦电阻器,一般约为 0.15pF 至 0.3pF,会影响结果。避免这一问题的方法是串联使用几个较低值的电阻器来创建一个具有低电容的大检测电阻器。每个电阻器的杂散电容表现为串联电容,因此串联使用的电阻器越多,总串联电容越小。 为此,电阻器被端对端焊接并允许弯曲到空气中,远离附近的物体以最大限度地减少杂散电容。对于此测量,五个 2MΩ 电阻器被端对端焊接。有关实际使用的电阻串的照片,请参见第 2 部分中的图 3 。

第二点是要注意电路的整体带宽并注意输出转换速率限制。当您找到极点频率时,最好再次短路检测电阻并确保幅度与原始参考频率 (~100mV) 相同,以验证你没有耗尽带宽或达到转换速率限制。 如果幅度不同,请增加检测电阻器的值或在输入端添加已知电容以降低极点频率(添加 20pF,然后从结果中减去 20pF)。任何类型的电容器都可用于此测试,因为泄漏并不重要。为避免压摆限制,请使用尽可能低的幅度以获得良好的结果。 总结我们大家都希望本教程能让你更好地理解亚皮安测量所面临的挑战。创造力是这些层面上最好的工具。与任何一个时间里挑战自然极限一样,要为轻微的挫折和电路或布局修改做好准备。

文章出处:【微信号:TT1827652464,微信公众号:云深之无迹】欢迎添加关注!文章转载请注明出处。

本人初如电子行业,今天有一个疑问需要请教各位大神,想请教一下GB4706.1和GB7000.1中的

互调、高效率的发展的新趋势,重点讨论了通信设施内模块与设备外模块的连接器设计与实现,主要讨论怎么来实现快插连接器的

检测 /

思路 /

图 /

安培表 /

残压半导体放电管 /

时出现的问题,并研究了屏蔽和防护方法的应用。在第 2 部分中,将研究元件选择怎么样影响